# Product Preview

# **Electric Field Imaging Device**

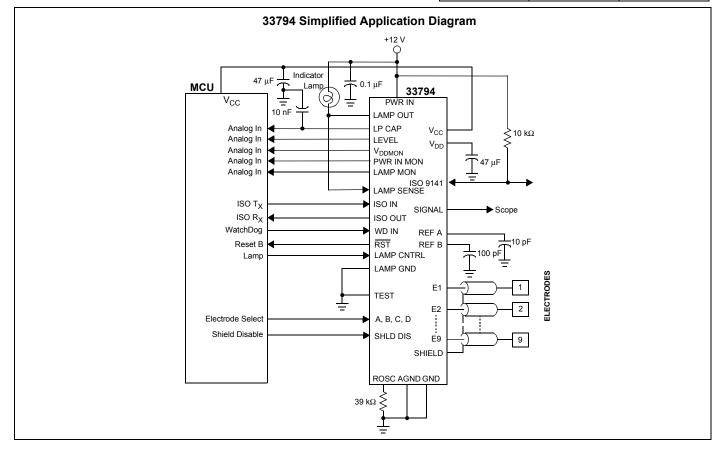

The 33794 is intended for applications where noncontact sensing of objects is needed. It contains circuitry necessary to generate a low level electric field and measure the loading of the field by objects in it. Support for a microcontroller unit (MCU) is also provided, as well as a physical layer communications interface. This allows the construction of a compact system consisting of this device, an MCU, and a few discrete components.

## Features

- · Supports up to 9 Electrodes and 2 References

- Shield Driver to Reduced Cable Capacitance Circuit •

- +5.0 V Regulator to Power External Circuit

- ISO 9141 Physical Layer Interface

- Lamp Driver Output

- · Watchdog and Power on Reset Timer

- High-Purity Sine Wave Generator Tunable with External Resistor

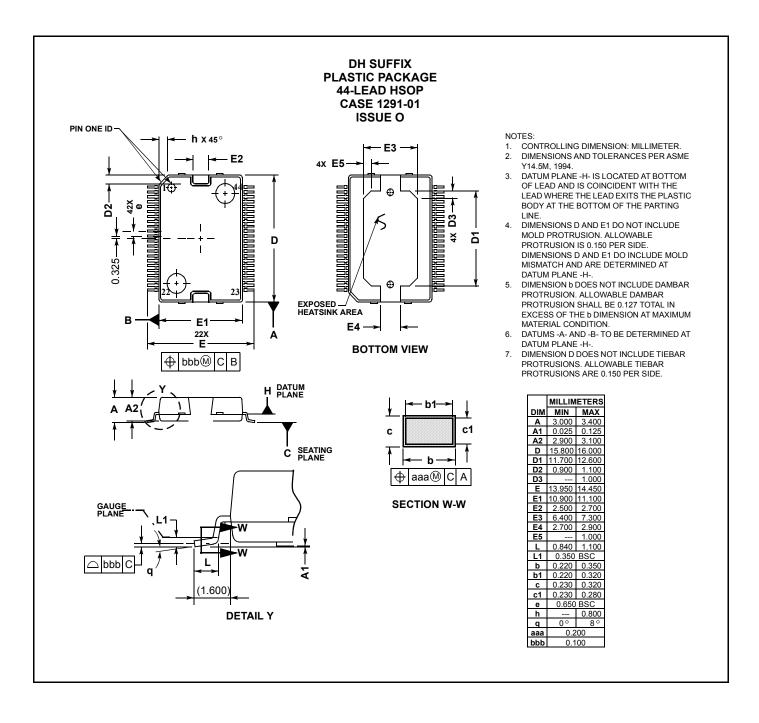

44-LEAD HSOP PLASTIC PACKAGE CASE 1291

# ORDERING INFORMATION

| Device    | Temperature<br>Range (T <sub>A</sub> ) | Package |

|-----------|----------------------------------------|---------|

| MC33794DH | -40 to +85°C                           | HSOP-44 |

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

OROLA

163\_com

ELECTRIC FIELD

**IMAGING DEVICE**

Rev 5, 08/2002

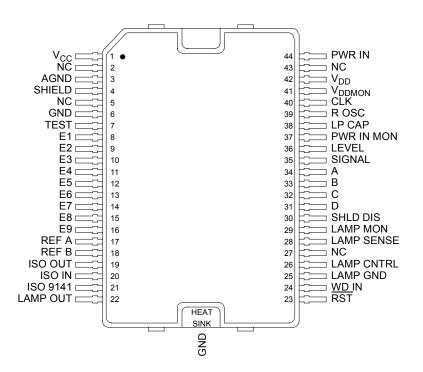

Note: Pins 2, 5, 27, and 43 are not used.

# **PIN FUNCTION DESCRIPTION**

| Pin Number   | Pin Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | V <sub>CC</sub> | This output pin requires a 47 $\mu F$ capacitor and provides a regulated 5.0 V for the MCU and for internal needs of the 33794.                                                                                                                                                                                                                                                                                                                                                         |

| 2, 5, 27, 43 | NC              | No connect. These pins may be used at some future date and should be left open.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3            | AGND            | This pin is connected to the ground return of the analog circuitry. This ground should be kept free of transient electrical noise like that from logic switching. Its path to the electrical current return point should be kept separate from the return for GND.                                                                                                                                                                                                                      |

| 4            | SHIELD          | This pin connects to cable shields to cancel cable capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6, Heat Sink | GND             | This pin and metal backing is the IC power return and thermal radiator/conductor.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7            | TEST            | This pin is normally connected to circuit ground. There are special operating modes associated with this pin when it is not at ground.                                                                                                                                                                                                                                                                                                                                                  |

| 8–16         | E1–E9           | These are the electrode pins. They are connected either directly or through coaxial cables to the electrodes for measurements. One of these electrodes can be selected at a time for capacitance measurement. All of the other unselected electrodes are grounded by an internal switch. The signal at the selected electrode pin is routed to the shield driver amplifier by an internal switch. All of the coaxial cable shields should be isolated from ground and connected SHIELD. |

| 17–18        | REF A–REF B     | These pins can be individually selected like E1 through E9. Unlike E1 through E9, these pins are not grounded when not selected. The purpose of these pins is to allow known capacitors to be measured. By using capacitors at the low and high end of the expected range, absolute values for the capacitance on the electrodes can be computed.                                                                                                                                       |

| 19           | ISO OUT         | This pin translates ISO 9141 receive levels to 5.0 V logic levels for the MCU.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20           | ISO IN          | This pin accepts data from the MCU to be sent over the ISO 9141 communications interface. It translates the 5.0 V logic levels from the MCU to transmit levels on the ISO 9141 bus.                                                                                                                                                                                                                                                                                                     |

| 21           | ISO 9141        | This pin connects to the ISO 9141 bus. It provides the drive and detects signaling on the bus and translates it from the bus level to logic levels for the MCU.                                                                                                                                                                                                                                                                                                                         |

#### **PIN FUNCTION DESCRIPTION**

| Pin Number | Pin Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | LAMP OUT           | This is an active low output capable of sinking current of a typical indicator lamp. One end of the lamp should be connected to a positive supply (for example, battery voltage) and the other side to this pin. The current is limited to prevent damage to the IC in the case of a short or surge during lamp turn-on or burn-out.                                                                                                                                                                                                                                                                         |

| 23         | RST                | This output is intended to generate the reset function of a typical MCU. It has a delay for power-on reset level detectors to force a reset when $V_{CC}$ is out-of-range high or low, and a watchdog timer that will force a reset if WD IN is not asserted at regular intervals. Timing is derived from the oscillator and will change with changes in the resistor attached to R OSC.                                                                                                                                                                                                                     |

| 24         | WD IN              | This pin must be asserted and deasserted at regular interval in order to prevent $\overline{RST}$ from being asserted.<br>By having the MCU program perform this operation more often the allowed time, a check that the MCU is<br>running and executing its program is assured. If this doesn't occur, the MCU will be reset. If the watchdog<br>function is not desired, this pin may be connected to CLK to prevent a reset from being issued.                                                                                                                                                            |

| 25         | LAMP GND           | This is the ground for the current from the lamp. The current into LAMP OUT flows out through this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26         | LAMP CNTRL         | This signal is used to control the lamp driver. A high logic level turns on the lamp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28         | LAMP SENSE         | This pin is connected to the LAMP pin. The voltage at this pin is reduced and sent to LAMP MON so the voltage at the lamp pin is brought into the range of the analog-to-digital converter (ADC) in the MCU.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29         | LAMP MON           | This pin is connected through a voltage divider to the LAMP SENSE pin. The voltage divider scales the voltage at this pin so that battery voltage present when the lamp is off is scaled to the range of the MCU ADC. With the lamp off, this pin will be very close to battery voltage if the lamp is not burned out and the pin is not shorted to ground. This is useful as a lamp check.                                                                                                                                                                                                                  |

| 30         | SHLD DIS           | This pin is used to turn off the shield signal. The purpose of doing this is to be able to detect that the shield signal is not working or the connection to the coax shields is broken. If either of these conditions exists, there will be little or no change in the capacitance measured when the SHLD DIS is asserted. If the SHIELD output is working and properly connected, the capacitance of the coax will not be cancelled when this pin is asserted and the measured capacitance will appear to change by approximately the capacitance between the center conductor and the shield in the coax. |

| 34–31      | A, B, C, D         | These input pins control which electrode or reference is active. Selection values are shown in Table 1, Electrode Selection, page 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 35         | SIGNAL             | This is the undetected signal being applied to the detector. It has a DC level with the low radio frequency signal superimposed on it. Care must be taken to minimize DC loading of this signal. A shift of DC will change the center point of the signal and adversely affect the detection of the signal.                                                                                                                                                                                                                                                                                                  |

| 36         | LEVEL              | This is the detected, amplified, and offset representation of the signal voltage on the selected electrode. Filtering of the rectified signal is performed by a capacitor attached to LP CAP.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 37         | PWR IN MON         | This is connected through a voltage divider to PWR IN. It allows reduction of the voltage so it will fall within the range of the ADC on the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 38         | LP CAP             | A capacitor on this pin forms a low pass filter with the internal series resistance from the detector to this pin. This pin can be used to determine the detected level before amplification or offset is applied. A 10 nF capacitor connected to this pin will smooth the rectified signal. More capacitance will increase the response time unnecessarily.                                                                                                                                                                                                                                                 |

| 39         | R OSC              | A resistor from this pin to circuit ground determines the operating frequency of the oscillator. The 33794 is optimized for operation around 120 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 40         | CLK                | This pin provides a square wave output at the same frequency as the internal oscillator. The edges of the square wave coincide with the peaks (positive and negative) of the sine wave.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 41         | V <sub>DDMON</sub> | This is connected through a voltage divider to $V_{DD}$ . It allows reduction of the voltage so it will fall within the range of the ADC on the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 42         | V <sub>DD</sub>    | A capacitor is connected to this pin to filter the internal analog regulated supply. This supply is derived from PWR IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **PIN FUNCTION DESCRIPTION**

| Pin Number | Pin Name | Description                                                                                                                                                                                                     |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44         | PWR IN   | 12 V power applied to this pin will be converted to the regulated voltages needed to operate the part. It is also converted to 5.0 V ( $V_{CC}$ ) and 8.5 V ( $V_{DD}$ ) to power the MCU and external devices. |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                 | Symbol              | Value       | Unit |

|----------------------------------------|---------------------|-------------|------|

| Peak PWR IN Voltage                    | V <sub>PINPK</sub>  | 40          | V    |

| Double Battery                         | V <sub>DBLBAT</sub> |             | V    |

| 1 minute maximum T <sub>A</sub> = 30°C |                     | 26.5        |      |

| ESD1 Voltage (All Pins) (Note 1)       | V <sub>ESD1</sub>   | 2000        | V    |

| ESD2 Voltage (All Pins) (Note 2)       | V <sub>ESD2</sub>   | 200         | V    |

| Storage Temperature                    | T <sub>STG</sub>    | -55 to +150 | °C   |

| Operating Ambient Temperature          | T <sub>A</sub>      | -40 to +85  | °C   |

| Operating Junction Temperature         | Т <sub>Ј</sub>      | -40 to +150 | °C   |

| Thermal Resistance                     |                     |             |      |

| Junction-to-Ambient (Note 3)           | $R_{\theta J-A}$    | 41          | °C/W |

| Junction-to-Case (Note 4)              | $R_{\theta J-C}$    | 0.2         | °C/W |

| Junction-to-Board (Note 5)             | $R_{\thetaJ}$ -B    | 3.0         | °C/W |

| Soldering Temperature (for 10 seconds) | T <sub>SOLDER</sub> | 260         | °C   |

Notes:

- 1. ESD1 performed in accordance with the Human Body Model (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500  $\Omega$ ).

- 2. ESD2 performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- 3. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance. In accordance with SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 4. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MILSPEC 883 Method 1012.1) with the cold plate temperature used for the case temperature.

- 5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

# STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under condition -40°C  $\leq T_{J} \leq$  150°C. Voltages are relative to GND unless otherwise noted.

| Characteristic                                                                                                          | Symbol               | Min   | Тур  | Мах   | Unit |

|-------------------------------------------------------------------------------------------------------------------------|----------------------|-------|------|-------|------|

| VOLTAGE REGULATORS                                                                                                      |                      |       |      |       |      |

| 5.0 V Regulator Voltage 7.0 V $\leq$ V_{PWR IN} $\leq$ 18 V, 1.0 mA $\leq$ I_L $\leq$ 75 mA $C_{FILT}$ = 47 $\mu F$     | V <sub>CC</sub>      | 4.75  | 5.0  | 5.25  | V    |

| Analog Regulator Voltage 9.0 V $\leq$ V_{PWR IN} $\leq$ 18 V C_{FILT} = 47 $\mu F$                                      | V <sub>Analog</sub>  | 8.075 | 8.5  | 8.925 | V    |

| V <sub>CC</sub> OUT-OF-RANGE VOLTAGE DETECTOR                                                                           |                      | 1     | 1    | 1     |      |

| 5.0 V Low Voltage Detector                                                                                              | $V_{LV5}$            | 4.0   | 4.52 | 4.72  | V    |

| 5.0 V High Voltage Detector                                                                                             | V <sub>HV5</sub>     | 5.26  | 5.55 | 5.83  | V    |

| 5.0 V Out-of-Range Voltage Detector Hysteresis                                                                          | V <sub>HYS5</sub>    | _     | 0.05 | -     | V    |

| ISO 9141 COMMUNICATIONS INTERFACE                                                                                       |                      | I     | 1    | 1     |      |

| Input Low Level (Note 6)                                                                                                | VIF <sub>INLO</sub>  | 0.30  | 0.33 | -     | V/V  |

| Input High Level (Note 6)                                                                                               | VIF <sub>INHI</sub>  | _     | 0.53 | 0.7   | V/V  |

| Input Hysteresis (Note 6)                                                                                               | VIF <sub>INHYS</sub> | -     | 0.2  | -     | V/V  |

| Output Low (Note 6)                                                                                                     | VIF <sub>OLO</sub>   | _     | -    | 0.2   | V/V  |

| Output High (Note 6)                                                                                                    | VIF <sub>OHI</sub>   | 0.8   | -    | -     | V/V  |

| Output Breakdown<br>I <sub>OUT</sub> = 20 mA                                                                            | VIFZ                 | 40    | _    | _     | V    |

| Output Resistance<br>I <sub>OUT</sub> = 40 mA                                                                           | RIF <sub>ON</sub>    | _     | 58   | _     | Ω    |

| Current Limit<br>Sinking current with V <sub>OUT</sub> < 0.3 V <sub>PWR IN</sub>                                        | IIF <sub>LIM</sub>   | 60    | 90   | 120   | mA   |

| Output Propagation Delay<br>Out to ISO 9141 C <sub>LOAD</sub> = 20 pF                                                   | TIF <sub>DLY</sub>   | _     | -    | 8.0   | μs   |

| ISO IN                                                                                                                  |                      | l     | 1    | 1     |      |

| Logic Output Low<br>I <sub>sink</sub> = 1.0 mA                                                                          | VIF <sub>OLO</sub>   | _     | _    | 1.0   | V    |

| Logic Output Pull-up Current<br>V <sub>OUT</sub> = 0 V                                                                  | lif <sub>PU</sub>    | 100   | _    | _     | μΑ   |

| Input to Output Propagation Delay ISO 9141 to ISO IN RL = 10 k $\Omega$ CL = 470 pF 7.0 V $\leq$ V_{PWR IN} $\leq$ 18 V | TIF <sub>DLY</sub>   | _     | _    | 5.4   | μs   |

Notes:

6. Ratio to V<sub>PWR IN</sub>.

## STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under condition  $-40^{\circ}C \le T_J \le 150^{\circ}C$ . Voltages are relative to GND unless otherwise noted.

| Characteristic                                                  | Symbol              | Min  | Тур  | Max | Unit            |

|-----------------------------------------------------------------|---------------------|------|------|-----|-----------------|

| OSC                                                             |                     |      |      |     |                 |

| OSC Frequency Stability (Note 7), (Note 8)                      | F <sub>STAB</sub>   | -    | -    | 10  | %               |

| OSC Center Frequency                                            | F <sub>OSC</sub>    |      |      |     | kHz             |

| $R OSC = 39 k\Omega$                                            |                     | -    | 120  | -   |                 |

| Harmonic Content (Note 7)                                       | OSCH <sub>ARM</sub> |      |      |     | dB              |

| 2nd through 4th Harmonic level                                  |                     | -    | -    | -20 |                 |

| 5th and higher                                                  |                     | -    | -    | -60 |                 |

| ELECTRODE SIGNALS                                               |                     |      |      |     |                 |

| Total Variance Between Electrode Measurements                   | ELV <sub>VAR</sub>  |      |      |     | %               |

| All C <sub>Load</sub> = 15 pF                                   |                     | -    | -    | 3.0 |                 |

| Electrode Maximum Harmonic level below Fundamental (Note 7)     | EL <sub>HARM</sub>  |      |      |     | dB              |

| 5.0 pF $\leq$ C <sub>Load</sub> $\leq$ 100 pF                   |                     | -    | -20  | -   |                 |

| Electrode Transmit Output Range                                 | EL <sub>TXV</sub>   |      |      |     | V               |

| 5.0 pF $\leq$ C <sub>Load</sub> $\leq$ 100 pF                   |                     | 1.0  | -    | 8.0 |                 |

| Receive Input Voltage Range                                     | RX <sub>V</sub>     | 0    | -    | 9.0 | V               |

| Grounding Switch on Voltage                                     | SW <sub>VON</sub>   |      |      |     | V               |

| I <sub>SW</sub> = 1.0 mA                                        |                     | -    | -    | 5.0 |                 |

| SHIELD DRIVER                                                   |                     |      | 1    | 1   | 1               |

| Shield Driver Maximum Harmonic level below Fundamental (Note 7) | SD <sub>HARM</sub>  |      |      |     | dB              |

| $10 \text{ pF} \le C_{Load} \le 500 \text{ pF}$                 |                     | -    | -20  | -   |                 |

| Shield Driver Output Level                                      | SD <sub>TXV</sub>   |      |      |     | V               |

| $0 \text{ pF} \le C_{\text{Load}} \le 500 \text{ pF}$           |                     | 1.0  | -    | 8.0 |                 |

| Shield Driver Gain Bandwidth Product (Note 7)                   | SD <sub>GBW</sub>   |      |      |     | MHz             |

| Measured at 120 kHz                                             |                     | -    | 4.5  | _   |                 |

| Shield Driver Input Range                                       | SD <sub>IN</sub>    | 0    | -    | 9.0 | V               |

| Grounding Switch on Voltage (Note 9)                            | SW <sub>VON</sub>   | -    | -    | 1.5 | V               |

| LOGIC I/O                                                       |                     |      |      |     | •               |

| CMOS Logic Input Low Threshold                                  | V <sub>THL</sub>    | 0.3  | _    | -   | V <sub>CC</sub> |

| Logic Input High Threshold                                      | V <sub>THH</sub>    | _    | -    | 0.7 | V <sub>CC</sub> |

| Voltage Hysteresis                                              | V <sub>HYS</sub>    | _    | 0.06 | _   | V <sub>CC</sub> |

| Input Current                                                   | I <sub>IN</sub>     |      |      |     | μA              |

| $V_{IN} = V_{CC}$                                               |                     | 10   | -    | 50  |                 |

| V <sub>IN</sub> = 0 V                                           |                     | -5.0 | -    | 5.0 |                 |

Notes:

- 7. Verified by design and characterization, not tested in production.

- 8. Does not include errors in external reference parts.

- 9. Current into grounded pin under test = 1 mA.

## STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under condition -40°C  $\leq T_J \leq$  150°C. Voltages are relative to GND unless otherwise noted.

| Characteristic                         | Symbol              | Min    | Тур     | Max    | Unit           |

|----------------------------------------|---------------------|--------|---------|--------|----------------|

| POR                                    |                     |        | •       | •      |                |

| POR Time-Out Period                    | T <sub>PER</sub>    | 9.0    | -       | 50     | ms             |

| WATCHDOG                               |                     |        |         | 1      | 1              |

| Watchdog Time-Out Period               | T <sub>WDPER</sub>  | 50     | 68      | 250    | ms             |

| Watchdog Reset Hold Time               | T <sub>WDHLD</sub>  | 9.0    | -       | 50     | ms             |

| SIGNAL DETECTOR                        |                     |        |         | 1      | 1              |

| Detector Output Resistance             | DET <sub>RO</sub>   | -      | 50 k    | _      | Ω              |

| LP CAP to LEVEL Gain                   | A <sub>REC</sub>    | 3.6    | 4.0     | 4.4    | A <sub>V</sub> |

| LP CAP to LEVEL Offset                 | V <sub>RECOFF</sub> | -3.3   | -3.0    | -2.7   | V              |

| LAMP DRIVER                            |                     |        |         |        |                |

| On Resistance                          | RLD <sub>DSON</sub> |        |         |        | Ω              |

| I <sub>IN</sub> = 400 mA               |                     | -      | 1.75    | 3.5    |                |

| Current Limit                          | ILD <sub>LIM</sub>  |        |         |        | Α              |

| V <sub>OUT</sub> = 1.0 V               |                     | 0.7    | -       | 1.7    |                |

| On-Voltage                             | VLD <sub>ON</sub>   |        |         |        | V              |

| I <sub>OUT</sub> = 400 mA              |                     | -      | -       | 1.4    |                |

| Breakdown Voltage                      | VLD <sub>Z</sub>    |        |         |        | V              |

| I <sub>OUT</sub> = 100 μA, Lamp off    |                     | 40     | -       | -      |                |

| Short Circuit to Battery Survival Time | T <sub>SCB</sub>    | 3.0    | -       | -      | ms             |

| VOLTAGE MONITORS                       |                     |        | •       |        |                |

| LAMP MON to LAMP SENSE ratio           | LMP <sub>MON</sub>  | 0.1950 | 0.20524 | 0.2155 | V/V            |

| PWR IN MON to PWR IN ratio             | PWR <sub>MON</sub>  | 0.2200 | 0.2444  | 0.2688 | V/V            |

| $V_{DD MON}$ to $V_{DD}$ ratio         | V <sub>DDMON</sub>  | 0.45   | 0.5     | 0.55   | V/V            |

| PIN/SIGNAL                       | D | С | В | Α |  |  |

|----------------------------------|---|---|---|---|--|--|

| Source (internal)                | 0 | 0 | 0 | 0 |  |  |

| E1                               | 0 | 0 | 0 | 1 |  |  |

| E2                               | 0 | 0 | 1 | 0 |  |  |

| E3                               | 0 | 0 | 1 | 1 |  |  |

| E4                               | 0 | 1 | 0 | 0 |  |  |

| E5                               | 0 | 1 | 0 | 1 |  |  |

| E6                               | 0 | 1 | 1 | 0 |  |  |

| E7                               | 0 | 1 | 1 | 1 |  |  |

| E8                               | 1 | 0 | 0 | 0 |  |  |

| E9                               | 1 | 0 | 0 | 1 |  |  |

| Ref A                            | 1 | 0 | 1 | 0 |  |  |

| Ref B                            | 1 | 0 | 1 | 1 |  |  |

| Internal OSC                     | 1 | 1 | 0 | 0 |  |  |

| Internal OSC after 22 k $\Omega$ | 1 | 1 | 0 | 1 |  |  |

| Internal ground                  | 1 | 1 | 1 | 0 |  |  |

| Reserved                         | 1 | 1 | 1 | 1 |  |  |

Table 1. Electrode Selection

# SYSTEM/APPLICATION INFORMATION

#### INTRODUCTION

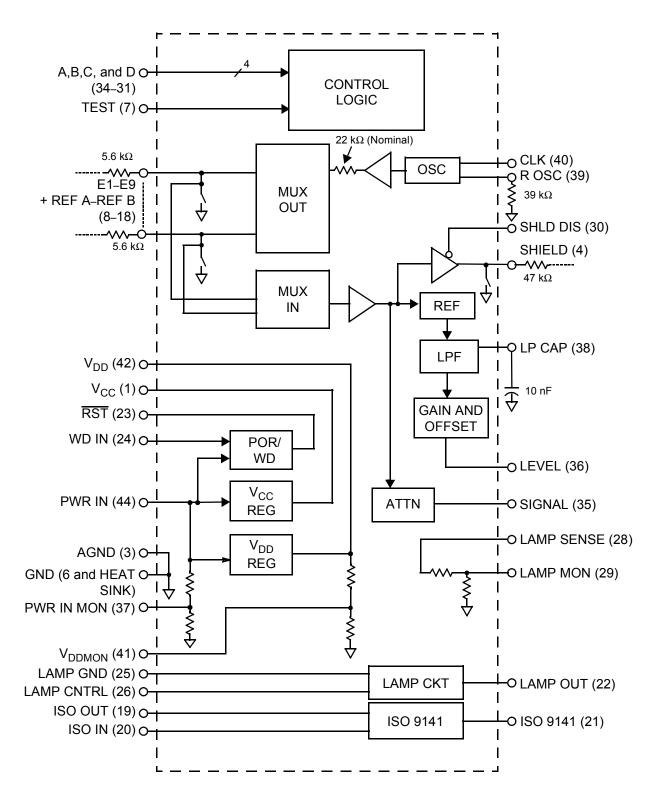

The 33794 is intended for use in detecting objects using an electric field. The IC generates a low radio frequency sine wave. The frequency is set by an external resistor and is optimized for 120 kHz. The sine wave has very low harmonic content to reduce potential interference at higher harmonically related frequencies. The internal generator produces a nominal 5.0 V peak-to-peak output that is passed through an internal resistor of about 22 kΩ. An internal multiplexer routes the signal to one of 11 pins under control of the ABCD input pins. A receiver multiplexer simultaneously connected to the selected electrode routes its signal to a detector, which converts the sine wave to a DC level. This DC level is filtered by an external capacitor and is multiplied and offset to increase sensitivity. All of the unselected electrode outputs are grounded by the device. The current flowing between the selected electrode and the other grounded electrodes plus other grounded objects around the

Refer to Figure 1, 33794 Internal Block Diagram, page 2, for block diagram and pin information.

#### osc

This section generates a high purity sine wave. The center frequency is controlled by a resistor attached to R OSC. The normal operating frequency is around 120 kHz. A square wave version of the frequency output is available at CLK. Timing for the power on reset and watchdog circuit are derived from this oscillator's frequency.

#### MUX OUT

This circuit directs the output of the sine wave to one of nine possible electrode outputs or two reference pins. All unused pins are automatically grounded. The selected output is controlled by the ABCD inputs.

#### **MUX IN**

This circuit connects the selected electrode, reference, or one of two internal nodes to an amplifier/detector. The selection is controlled by the ABCD inputs and follows the driven electrode/reference when one is selected.

#### RECT

This circuit detects the level from MUX IN by offsetting the midpoint of the sine wave to zero volts and inverting the waveform when it is below the midpoint. It is important to avoid DC loading of the signal, which would cause a shift in the midpoint voltage of the signal from the MUX IN.

# LPF

The rectified sine wave is filtered by a low pass function in the LPF formed by an internal resistance and an external electrode causes a voltage drop across the internal resistance. Objects brought into or out of the electric field change the current and resulting voltage at the IC pin, which in turn reduces the voltage at LP CAP and LEVEL.

A shield driver is included to minimize the effect of capacitance caused by using coaxial cables to connect to remote electrodes. By driving the coax shield with this signal, the shield voltage follows that of the center conductor, significantly reducing the effective capacitance of the coax and maintaining sensitivity to the capacitance at the electrode.

The 33794 is made to work with and support a microcontroller. It provides two voltage regulators, a power-on-reset/out-of-range voltage detector, watchdog circuit, lamp driver and sense circuit, and a physical layer ISO 9141 communications interface.

# **BLOCK DIAGRAM COMPONENTS**

capacitance attached to LP CAP. The nominal value of the internal resistance is 50 k $_{\Omega}$ . The value of the external capacitor is selected to provide filtering of noise while still allowing the desired settling time for the detector output. A 10 nF capacitor would allow 99% settling in less than 5 ms.

#### GAIN and OFFSET

This circuit multiplies the detected and filtered signal by a gain and offsets the result by a DC level. This results in an output range that covers 1.0 V to 4.0 V for capacitive loading of the field in the range of 10 pF to 100 pF. This allows higher sensitivity for a digital-to-analog converter with a 0 V to 5.0 V input range.

## ATTN

This circuit passes the undetected signal to SIGNAL for external use.

## LAMP CKT

This section controls the operation of the LAMP OUT pin. When LAMP CNTRL is asserted, LAMP OUT is pulled to LAMP GND. If one side of an indicator lamp or LED (with appropriate current setting resistor) is connected to a positive voltage source and the other is connected to LAMP OUT, and LAMP GND is connected to ground, the lamp will light. This circuit provides current limiting to prevent damage to itself in the case of a shorted lamp or during a high surge condition typical of an incandescent lamp burnout.

## ISO 9141

This circuit connects to an ISO 9141 bus to allow remote communications. ISO IN is data from the bus to the MCU and ISO OUT is data to drive onto the bus from the MCU.

#### POR/WD

This circuit is a combined power on reset and watchdog timer. The RST output is held low until a certain amount of time after the V<sub>CC</sub> output has remained above a minimum operating threshold. If V<sub>CC</sub> falls below the level at any time, RST is pulled low again and held until the required time after V<sub>CC</sub> has returned high. An overvoltage circuit is also included, which will force a reset if V<sub>CC</sub> rises above a maximum voltage. The watchdog function also can force RST low if too long an interval is allowed to pass between positive transitions on WD IN.

#### V<sub>cc</sub> REG

This circuit converts an unregulated voltage from VIN to a regulated 5.0 V source, which is used internally and available for other components requiring a regulated voltage source.

The 33794 is intended to be used where an object's size and proximity are to be determined. This is done by placing electrodes in the area where the object will be. The proximity of an object to an electrode can be determined by the increase in effective capacitance as the object gets closer to the electrode and modifies the electric field between the electrode and surrounding electrically common objects. The shape and size of an object can be determined by using multiple electrodes over an area and observing the capacitance change on each of the electrodes. Those that don't change have nothing near them, and those that do change have part of the object near them.

The voltage measured is an inverse function of the capacitance between the electrode being measured and the surrounding electrodes and other objects in the electric field surrounding the electrode. Increasing capacitance results in decreasing voltage. The value of series resistance (22 k $\Omega$ ) was chosen to provide a nearly linear relationship at 120 kHz over a range of 10 pF to 100 pF.

The measured value will change with any change in frequency, series resistance, driving voltage, or detector sensitivity. These can change with temperature and time. The proper use of REF A and REF B will allow much of the changes to be compensated for.

A typical measurement algorithm would start by measuring the voltage for two known value capacitors (attached to REF A and REF B). The value of these capacitors would be chosen to  $V_{CCMON}$  is a divided output from  $V_{CC},$  which allows a 0 V to 5.0 V ADC to be used to measure  $V_{CC}.$

## V<sub>DD</sub> REG

This is a regulator for analog devices that require more than 5.0 V. This is used by the device and some current is available to operate op-amps and other devices. By having this higher voltage available, some applications can avoid the need for a rail-to-rail output amplifier and still achieve the 0 V to 5.0 V output for a digital-to-analog converter input.  $V_{DDMON}$  is a divided output from  $V_{DD}$ , which allows a 0 V to 5.0 V ADC to measure  $V_{DD}$ .

## **CONTROL LOGIC**

This contains the logic that decodes and controls the MUXs and some of the test modes.

# APPLICATION INFORMATION

be near the minimum and maximum values of capacitance expected to be seen at the electrodes. These reference voltages and the known capacitance values are then used with the electrode measurement voltage to determine the capacitance seen by the electrode. This method can be used to detect short- and long-term changes due to objects in the electric field and significantly reduce the effect of temperatureand time-induced changes.

The 33794 does not contain an ADC. It is intended to be used with an MCU that contains one. Offset and gain have been added to the 33794 to maximize the sensitivity over the range of 0 pF to 100 pF. An 8-bit ADC can resolve around 0.4 pF of change and a 10-bit converter around 0.1 pF. Higher resolution results in more distant detection of smaller objects.

DC Loading on the electrodes should be avoided. The signal is generated with a DC offset that is more than half the peak-topeak level. This keeps the signal positive above ground at all times. The detector uses this voltage level as the midpoint for detection. All signals below this level are inverted and added to all signals above this level. Loading of the DC level will cause some of the positive half of the signal to be inverted and added and will change the measurement.

If it is not possible to assure that the electrodes will always have a high DC resistance to ground or a voltage source, a series capacitor of about 10 nF should be connected between the IC electrode pins and the electrodes.

# PACKAGE DIMENSIONS

# NOTES

# NOTES

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2002

#### HOW TO REACH US:

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution: P.O. Box 5405, Denver, Colorado 80217.

#### 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tao Po, N.T., Hong Kong. 852-26668334

TECHNICAL INFORMATION CENTER: 1-800-521-6274

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM 电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: <u>http://www.pc-ps.net/</u>

商斯达电子元器件网: <u>http://www.sunstare.com/</u>

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/

传感器销售热线:

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83370250 83376489 83376549 83607652 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: <u>SUNS8888@hotmail.com</u>

邮编: 518033 E-mail:<u>szss20@163.com</u> QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。 北京分公司:北京海淀区知春路132号中发电子大厦3097号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

- 上海分公司:上海市北京东路 668 号上海賽格电子市场 2B35 号

- TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司:西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382